Rozšíření ve výpočetních jednotkách a prohloubení „okna“

Procesory Intel Alder Lake budou asi největší hardwarová událost letoška. Jsou ještě přes dva měsíce daleko, ale už jsme dostali snad nejvíc očekávané info: Intel odhalil architekturu jader těchto CPU. Ta slibuje velké navýšení výkonu – půjde o jeden z největších architektonických skoků v x86 procesorech. Například poprvé přináší šest paralelních dekodérů a další posílení IPC, čímž Intel jde podobou cestou jako účinná jádra Applu.

Jako jsme vypíchli posílení dekodérů symbolicky ukazující, jak architektura Golden Cove kráčí cestou rozšíření jádra, lze to samé udělat u výpočetních jednotek (backendu), i když tam to možná není tak nápadné. Zvyšování IPC je ale hodně patrné na hloubce out-of-order bufferů a front. V těch procesor může držet více operací, díky čemuž se nezadrhne při různých zdrženích (třeba když chybí data z paměti, špatně se odhadne větvení). Také se pomocí těchto bufferů optimalizuje výkon tím, že se operace provádí v jiném pořadí, než v jakém je předpokládá program.

To druhé je hlavní podstata tzv. out-of-order procesorů: přehazováním instrukcí se dá docílit toho, že v jednom cyklu uděláte víc operací, protože vás tolik neomezují závislosti dat mezi instrukcemi – pokud nemáte tři nebo čtyři (nebo teď až šest) nezávislých instrukcí, abyste využili všechny dostupné jednotky, můžete se podívat do budoucích částí následujících v kódu pro takové instrukce, které na těch současných nezávisí a můžete si je tedy spočítat dopředu. Toto je stěžejní způsob, kterým procesory dosahují vyššího IPC. Ale pro toto zlepšení výkonu dosaženého v jednom cyklu je třeba, aby procesor při optimalizaci měl k dispozici co nejdelší kus kódu, z něhož by instrukce mohl brát a přehazovat je. Velikost tohoto tzv. „okna“ určuje fronta Re-Order Buffer (ROB).

A právě Re-Order Buffer možná je druhou z největších změn spolu s oním posílením dekodérů (a s nimi spojeného Fetche) – a asi ne náhodou je také velikost Re-order Bufferu další věcí, v níž vynikají architektury procesorů Apple s mimořádně vysokým IPC. Intel je zde do značné míry následuje. V architektuře Skylake měl ROB hloubku 224 položek (instrukcí, přesněji μOPů) a už Ice/Tiger/Rocket Lake (architektury Sunny/Willow/Cypress Cove) to výrazně navýšilo na 352 položek. Alder Lake/Golden Cove jde ještě dál a zvětšuje Re-order Buffer až na 512 položek.

Je třeba říct, že Apple je pořád dál, odhaduje se, že ROB u jeho současné architektury Firestorm má až 630 instrukcí. Nicméně relativní zvětšení je u Golden Cove hodně velké (takto vysoké asi většina hadačů neočekávala) a lze přitom předpokládat, že bude dál pokračovat v následujících architekturách. Zvětšování ROB není zadarmo; mělo by stát tranzistory, ale také spotřebu navíc, takže implementovat ho efektivně není asi vůbec lehké. Je zajímavé, že třeba AMD Zen 3 má pořád ROB s hloubkou jen 256 položek (přesto jádro ve výsledku má výkon jako Tiger Lake s hloubkou 352 – jak vidíte, výkon CPU nikdy neurčuje jen jediný izolovaný parametr). Ale zde je asi jasné, že AMD bude u budoucích architektur „okno“ ROB také zvětšovat.

Větší potenciál v backendu

Podobně jako u Fetche a dekódování jde zvětšení ROB ruku v ruce se zvětšením počtu výpočetních jednotek. Dává smysl tyto dva aspekty posilovat naráz, protože s větším oknem je větší šance využít víc jednotek.

Intel u Golden Cove dál používá svou dlouholetou koncepci (jdoucí až k Pentiu Pro), kdy jsou výpočetní jednotky sdružené za několika porty, do nichž scheduler rozesílá instrukce a na jednom portu je více jednotek, které pak nelze použít v jednom cyklu současně. Scheduler je jen jeden unifikovaný jak pro klasické, tak pro FPU a SIMD instrukce, jejichž jednotky se také skrývají za stejnými porty. Hodně konkurenčních jader (ARM, ale i například AMD) má tuto část rozdělenou a běžné aritmetickologické operace mají jeden klastr jednotek a svůj vlastní scheduler nebo schedulery a instrukce a jednotky SIMD jsou zase ve své vlastní oddělené části s vlastním schedulerem. Je zajímavé, že malé jádro procesorů Alder Lake (Gracemont) už má architekturu s oddělenými SIMD/FPU porty také, ale Golden Cove ne.

Golden Cove zvyšuje počet paralelních portů, a to na 12 z 10 u předchozí architektury (v Ice/Tiger/Rocket Lake, jádro Skylake jich mělo 8). Tím se zvyšuje počet operací, které procesor může teoreticky provést najednou nárazově z plného scheduleru (předchozí části jsou ale, jak jsme již viděli, stavěné na maximum šesti operací za cyklus, takže trvale udržitelné toto maximum 12 není).

Poprvé pět ALU

ALU neboli aritmeticko-logické celočíselné jednotky se skrývají za porty 0, 1, 5, 6 a pak za novým portem 10, který přidává pátou ALU k dosavadním čtyřem. To také znamená, že Golden Cove bude v říši x86 procesorem s největší šířkou. Pro srovnání Zen až Zen 3 mají čtyři ALU, Apple se dostal na šest.

Všech pět těchto portů také podporuje instrukci LEA (Load Effective Address), která je velmi často používaná – původně slouží pro obsluhu paměti, ale dá se užitečně použít k aritmetice a kompilátory ji v také takto produkují. Všech pět portů podporuje LEA s latencí jeden cyklus (je tedy hotová v příštím cyklu).

Další komplexnější instrukce ale mají omezenější propustnost. Násobení je zřejmě na dvou portech, bitové posuny také a také pro zpracování větvení (JMP) jsou dvě jednotky. Celočíselné dělení umí jedna jednotka.

Silnější AGU pro lepší paměťový výkon

Load-store či AGU jednotky jádra provádějící čtení a zápisy do paměti (respektive cache) jsou v Golden Cove také posílené. Procesor má místo čtyř AGU teď pět (porty 2, 3, 7, 8 a pátá je na druhém nově přidaném portu 11). Tři jednotky jsou Load a dvě Store, takže jádro Golden Lake podporuje tři čtení z paměti a zároveň dva zápisy do paměti za cyklus. Tři čtení a dva zápisy jsou stejná maxima, jako má AMD Zen 3, ale ten má jen tři AGU a může tedy udělat jen maximálně tři operace za cyklus: tři čtení, nebo dva zápisy a jedno čtení, nebo dvě čtení a jeden zápis. Tento subsystém tedy má Zen 3 slabší. Vedle toho má jádro také dva separátní porty jen pro ukládání dat (port 4 a 9), což je převzaté z předchozích architektur.

Nejde tu ovšem jen o počet operací, ale v případě náročných výpočtů také o propustnost, která je proti Zenu 3 až dvojnásobná. Běžná verze Golden Cove v procesorech Alder Lake by měla umět provést tři 256bitová čtení z L1 cache (odpovídající registru/vektoru AVX/AVX2) za cyklus (tedy propustnost 768b/cyklus, což by mělo být 50% zlepšení proti předchozímu jádru). Verze jádra Golden Cove s podporou AVX-512 by měla umět také dvě 512bitová čtení (odpovídající šířce registru/vektoru AVX-512) naráz, čímž by jádro dokázalo při výpočtech krmit jednotky daty s propustností 1 Kb v každém cyklu.

L1 cache samotná nemá přímo změny v kapacitě nebo asociativitě, stále je 48KB (což zavedla předchozí architektura v generaci Ice Lake/Sunny Cove). Ovšem výkon paměťového subsystému byl zlepšen dalšími cestami. Fill buffery L1 cache byly posílené z 12 na 16, byl vylepšený prefetch do L1 cache a také byl zvětšen TLB L1 Cache pro data z 64 na 96 položek. Vše toto by mělo zlepšovat výkon. Pokud dojde k TLB missu, pak také bude procesor hledat data na dalších úrovních paměťového subsystému rychleji, protože Intel zvýšil počet page walkerů ze dvou na čtyři (v tomhle je ovšem méně agresivní než konkurence – AMD u Zenu 3 zvýšilo počet ze dvou na šest).

Intel uvádí také, že byly prohloubeny také buffery pro operace čtení a zápisu z registrů do L1 cache, ale u nich není řečeno, jaké jsou teď jejich přesné velikosti. Procesor má také rychleji vyhodnocovat závislosti mezi paměťovými operacemi (tzv. Memory Disambiguation) a tím umožnit jejich rychlejší vykonání mimo pořadí. Celkově díky těmto zlepšením má jádro Golden Cove mít sníženou efektivní latenci čtení z L1 cache.

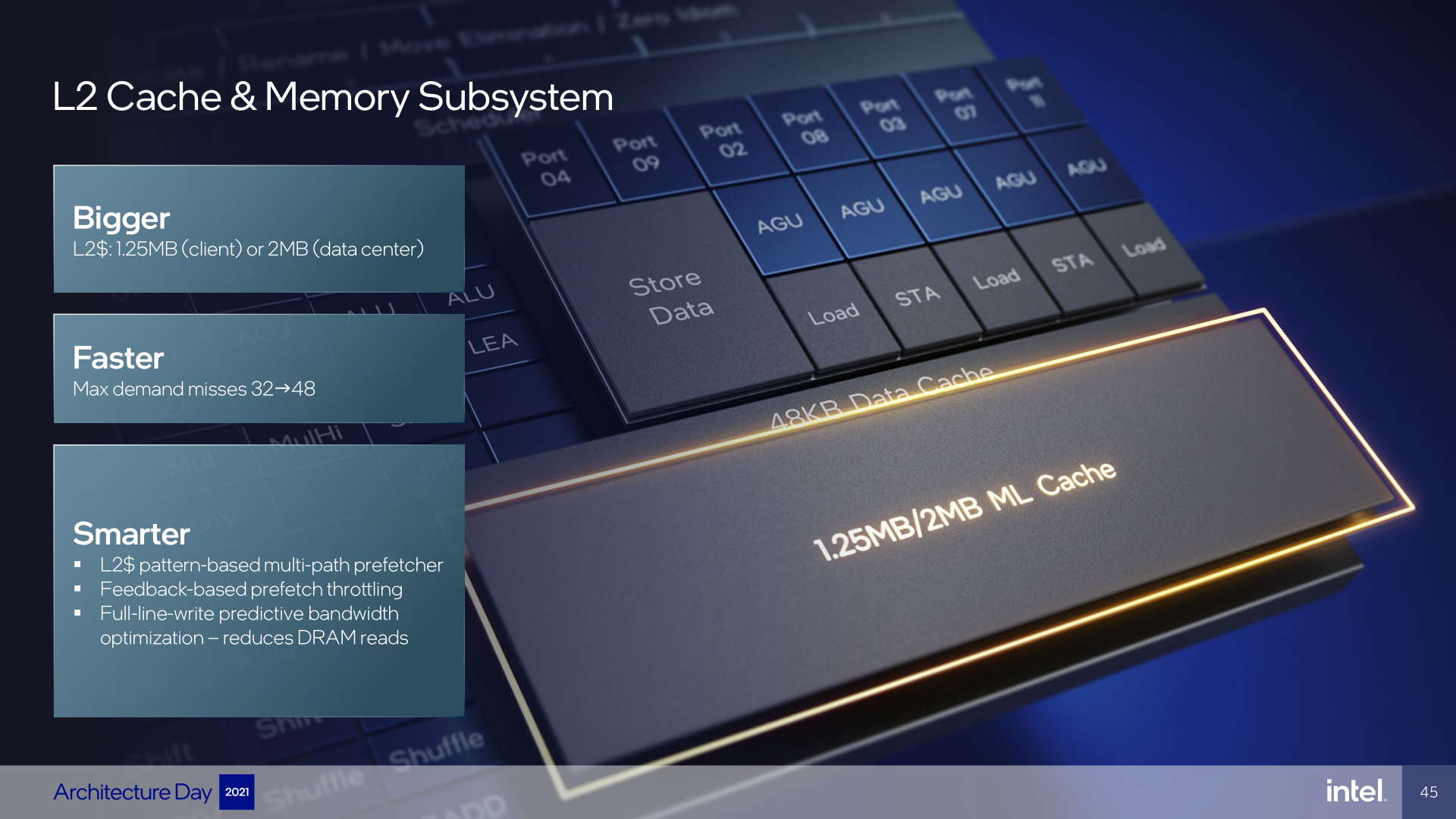

Také u L2 cache pak nastala zlepšení. Zvládá obsluhovat více paralelních požadavků na data z dalších úrovní paměti, když se v L2 nenajdou. Zatímco předchozí architektury mohly mít rozjeto 32 takových požadavků najednou, u Golden Cove jich lze paralelně mít až 48. Toto by mělo zlepšovat paměťový výkon a propustnost, kterou dokáže z RAM vytáhnout jedno vlákno/jádro. Jde mimochodem o další z parametrů, v kterém byla jádra Apple napřed před Intelem a AMD, takže nyní se jim asi Golden Cove může přiblížit. L2 cache má i účinnější prefetcher, který se umí podle zpětné vazby zpomalit, aby konzumoval méně propustnosti a uvolnil ji tak pro jiné operace. Došlo i na nějaká další vylepšení (Full-line-write predictive bandwidth optimisation).

Kapacita L2 cache je stejná jako u Tiger Lake/Willow Cove, tedy 1,25 MB pro jedno jádro (proti Rocket Lake, které ještě má jenom 512KB L2 cache, je to ale velké zvětšení – byť u Tiger Lake se nezdálo, že by mělo moc velký vliv). Serverová verze v procesorech Sapphire Rapids bude mít přidáno dalších 768 KB, stejně jako to Intel udělal v předchozích generacích serverových jader, takže bude celkově mít 2 MB L2 cache v každém jádru.

Článek pokračuje v další kapitole.

- Contents

- Architektura Golden Cove: historicky nejvýkonnější frontend u x86

- Rozšíření ve výpočetních jednotkách a prohloubení „okna“

- FPU a SIMD: AMX v serverech, Alder Lake přijde o AVX-512

- Rozšíření jádra získalo o 19 % vyšší výkon při stejném taktu

Oprava chyby v článku: bylo špatně napsané srovnání s počtem AGU a load/store operací za cyklus u Zenu 3 (ten má jen 3 AGU a může tedy udělat jen maximálně tři operace za cyklus: tři čtení, nebo dva zápisy a jedno čtení, nebo dvě čtení a jeden zápis, kdežto Golden Cove má 5 AGU umí 3 čtení a zároveň 2 zápisy).