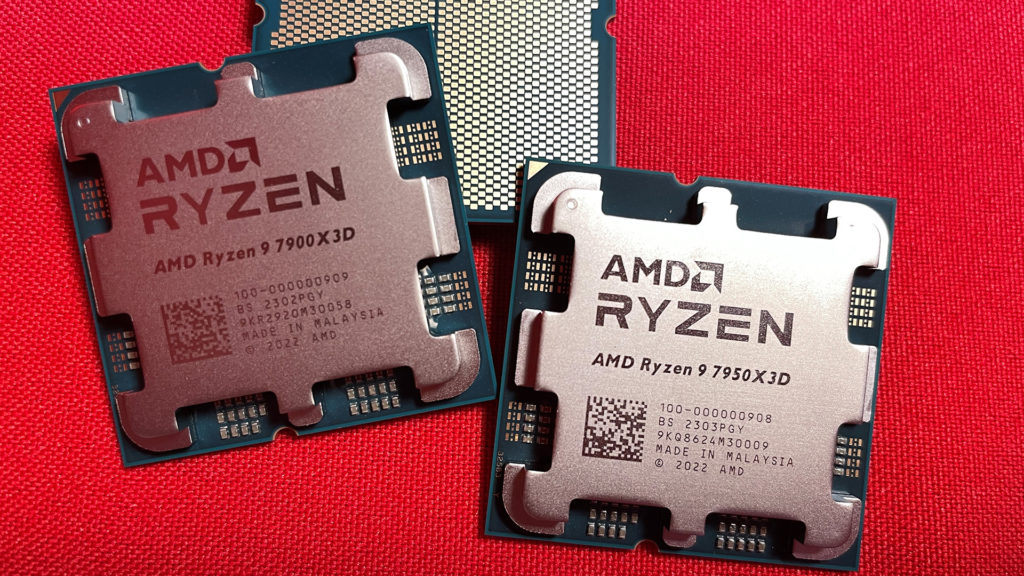

Last day of February, AMD started selling the Ryzen 7000 processors with 3D V-Cache, the chiplet technology increasing L3 cache capacity. Prior generation (Ryzen 7 5800X3D) proved that this benefited gaming, and it looks like the same is true now. Ryzen 7000s are aimed specifically at gaming PCs, and according to reviews, they seem to have surpassed Intel’s Raptor Lake processors in that and are now holding the gaming performance crown.

The basic concept of the Ryzen 7000X3D follows on from how the Ryzen 7 5800X3D was built. The processor reuses the usual IO chiplet and substrate, but one of the CPU Core Compex chiplets is special – the silicon is thinned down, has the so-called TSV channels hollowed out through it and copper wiring is routed through them connecting to second chiplet on top which contains additional L3 cache capacity, which transparently expands its original L3 cache from 32 MB to 96 MB. This layer is then facing the usual metal heat spreader covering all the dies, so the final processor looks as any usual AM5 SKU.

3D V-Cache is a 7nm chiplet, but it’s new silicon

The peculiarity is that the cache is produced by a different manufacturing process. AMD has confirmed that this chiplet is 7nm, while the CPU chiplet underneath containing Zen 4 cores is 5nm. This allows the cache die to be cheaper to manufacture. The chiplet is a bit larger than it would be with a 5nm process owing to that, but the cost is apparently still lower. However, this is not the same cache chiplet that was used in Zen 3, but a new and improved design. AMD says it has managed to reduce its area from 41 mm² to 36 mm², although it has roughly the same number of transistors (4.7 billion is claimed for both versions).

Transistor density has increased significantly from about 114 to 130 million transistors per square millimeter. Ironically, this is a higher transistor density than even the 5nm CPU chiplet with Zen 4 cores has. That’s because libraries achieving high transistor density were used for the V-Cache, which is mostly SRAM, while different, higher performance libraries were used for the CPU chiplet.

In addition, logic gates, especially those built for high power and clock speed, always have much lower density than the process achieves for dense SRAM cells. If the V-Cache circuits were implemented in the same fashion with libraries optimized for the lowest area but on the 5nm process, then the result would be smaller still than on the N7 node.

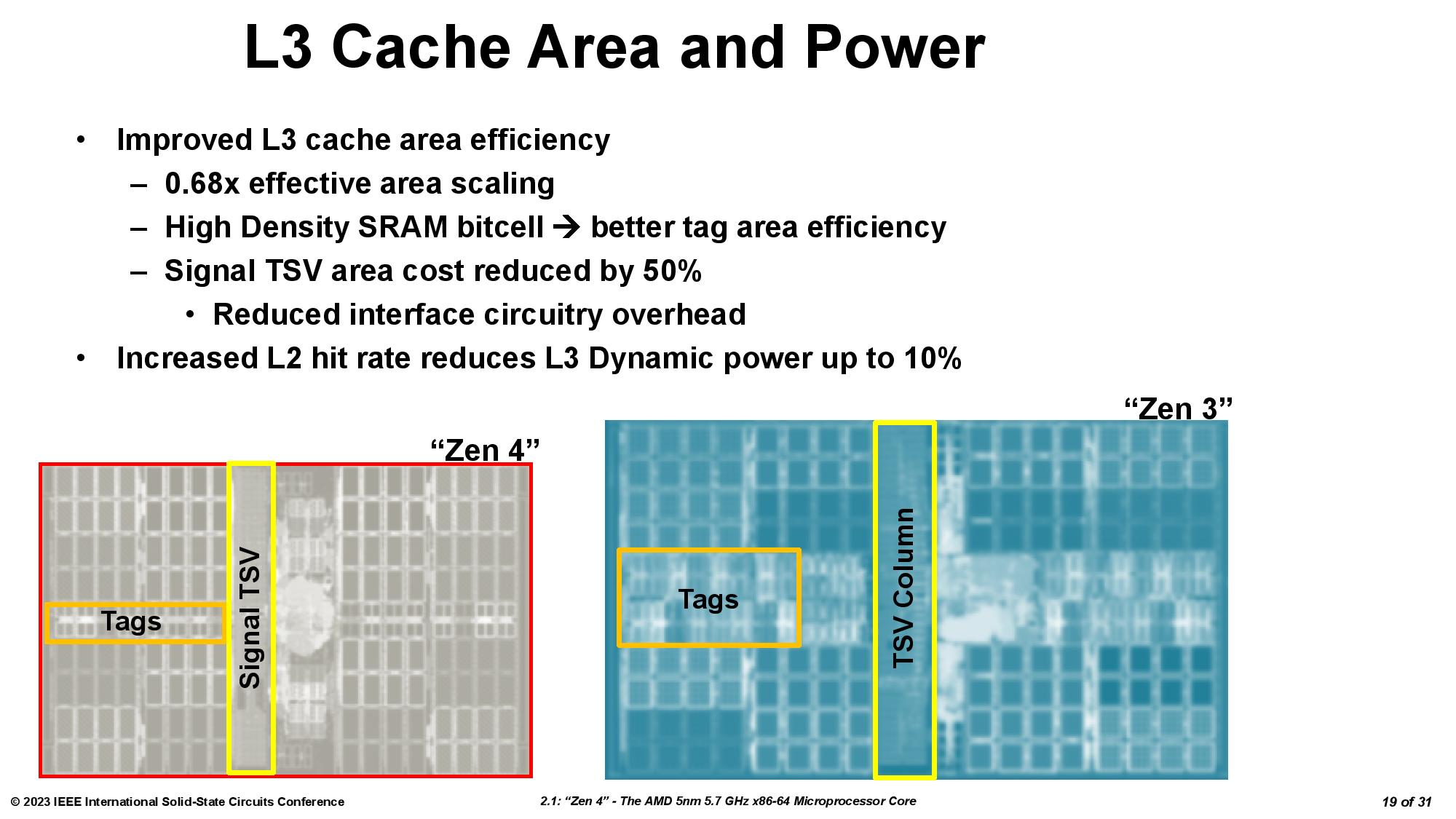

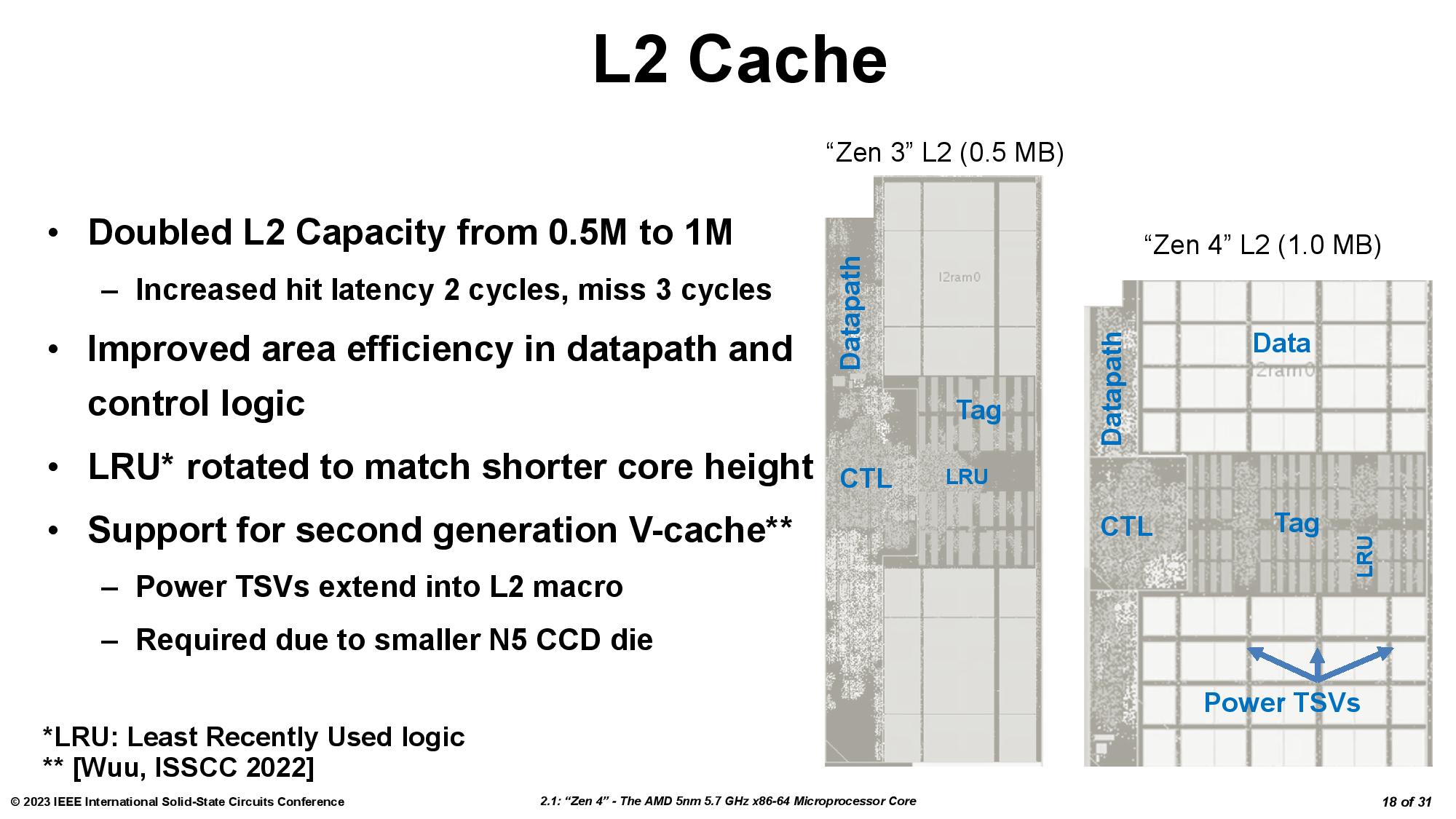

Because the underlying CPU chiplet has been shrunk, the 3D V-Cache die in the Ryzen 7000X3D must use a different layout of contacts (although the area they occupy has reportedly been reduced, too). In the Zen 3 generation, the contacts sat above the L3 cache of the CPU chiplet, through which vertical channels (called TSVs) were made that contain copper wires that connect the copper layers on the bottom of the CPU chiplet to the copper layer on the bottom of the V-Cache chiplet. For Zen 4, the layout had to be changed. The TSVs now not only run through the L3 cache, part of the TSVs with the wires providing power supply also go through the SRAM blocks of the L2 cache of the Zen 4 cores. The signal (data, control) wires go through the L3 cache.

This change by itself means that AMD couldn’t use the same chiplet as in the previous generation (this was previously speculated). That possibility is also disproved by the fact that the area of the cache chiplet has been reduced, naturally.

Zenu 4’s V-Cache has 25% higher bandwidth

The new chiplet used for Zen 4 also achieves higher performance, at least in bandwidth, which should suit HPC applications. While the previous generation managed to achieve a bandwidth of up to 2 TB/s between the CPU chiplet and the V-Cache, it is now up to 2.5 TB/s. On the other hand, latency is reportedly slightly higher, increasing by 4 cycles (which means single-digit percent difference in the context of L3 cache latency).

The entire 3D V-Cache is on the same power plane as the processor cores. It cannot use separate lower voltage and clock speeds differnet from the Zen 4 cores. According to the Tom’s Hardware website, at least in the case of the Ryzen 9 7950X3D processor, the maximum clock speed achieved on the CPU chiplet with 3D V-Cache is 5.25 GHz in single-threaded and 4.85 GHz in multi-threaded workloads, and the maximum voltage is 1.152 V. These are not spec values, but values measured during the review, so they may not be 100% valid at all times and for all specimens. In contrast, the second chiplet of the processor without V-Cache reached clock speeds of up to 5.75 GHz (single-threaded) and 5.30 GHz (multi-threaded), and the maximum voltage was 1.384 V.

Due to the fact that chiplets with 3D V-Cache must not be fed as high voltages, classic overclocking by changing multipliers and clock speeds will not be allowed on these processors again, same as in the prior generation. However, partial OC is possible – the Precision Boost Overdrive features are enabled, which allow performance to be increased within the normal boost operation, as well as the Curve Optimizer to allow undervolting. It is of course possible to overclock DDR5 memory.

How to ensure optimal performance: drivers, BIOS and interaction with Windows

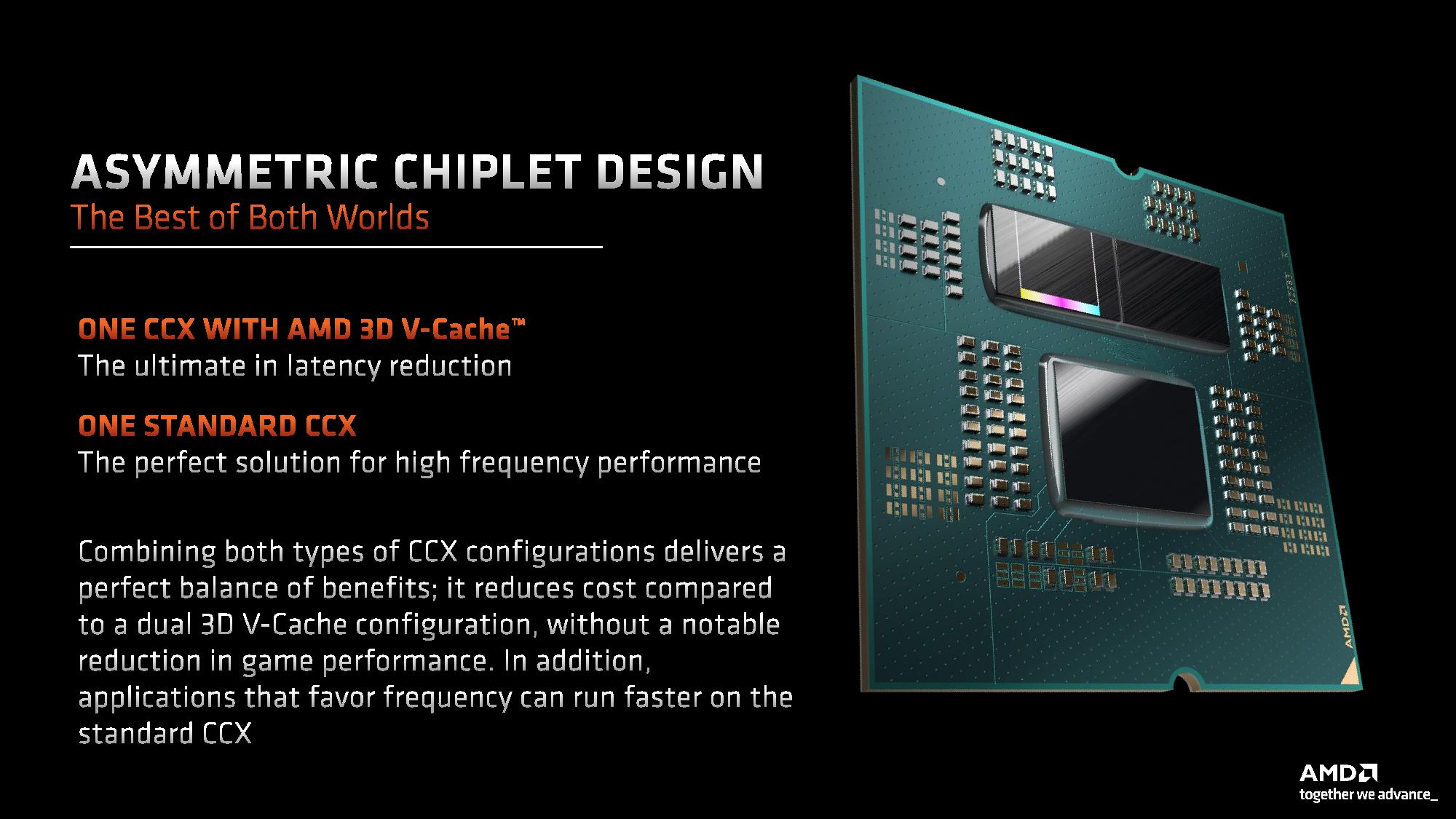

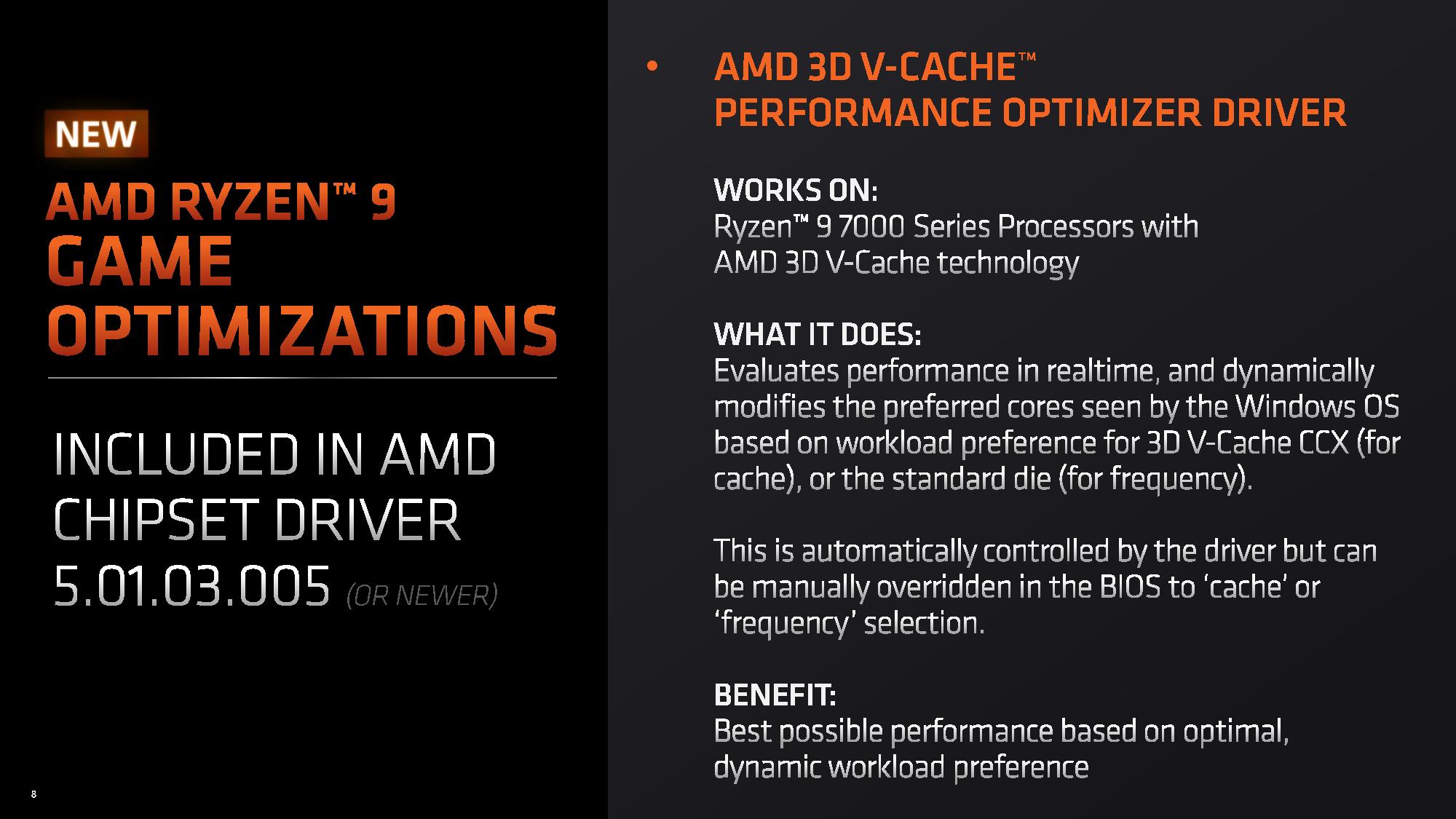

As we wrote during the processor unveiling, placing the V-Cache on only one of the two CPU chiplets has the effect that for 12 and 16-core processors, one half of the CPU has 96MB of L3 cache and relatively lower maximum clock speeds, while the other half has higher clock speeds but only 32MB of L3 cache. For ideal performance in games, they need to be placed on the cores of the chiplet with 3D V-Cache, and vice versa for applications (but this is not entirely without exceptions). Like Intel’s hybrid processors, this needs special management.

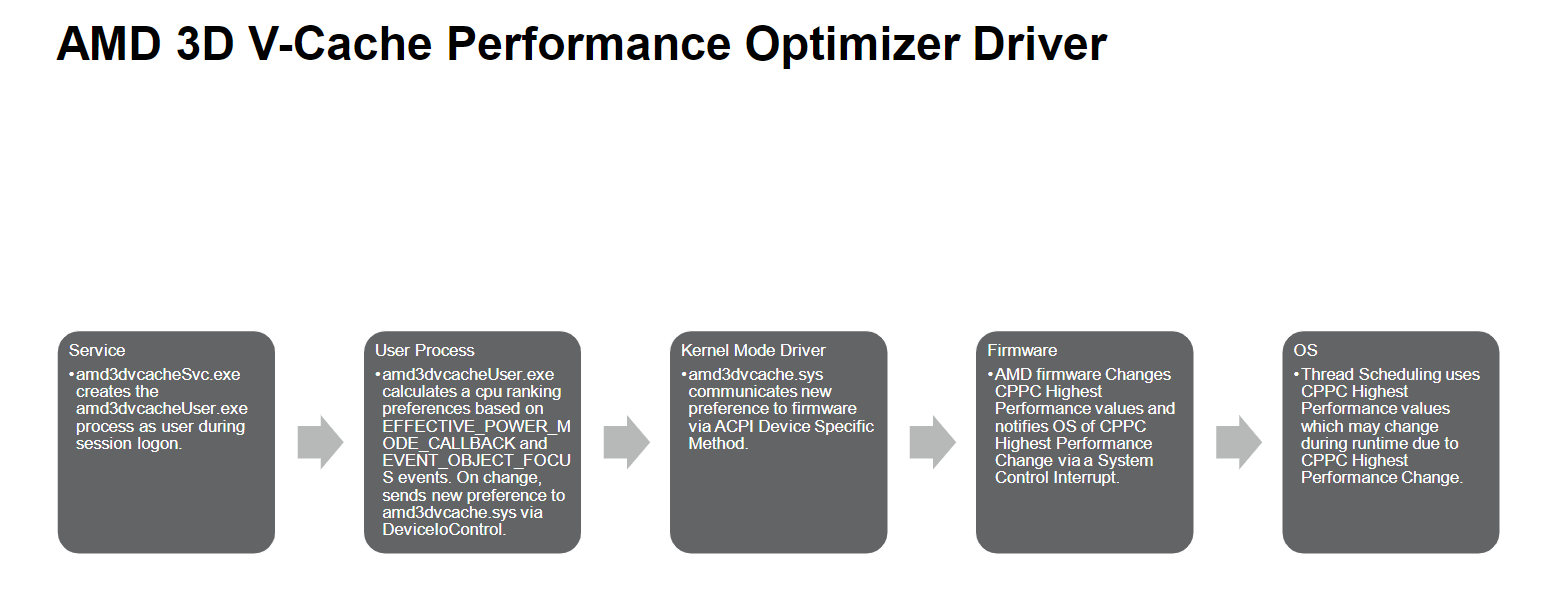

With Ryzen 7000X3D, this is ensured on several levels. The first requirement is having a sufficiently updated BIOS (UEFI) in the motherboard. Then also updating the chipset drivers (which are really the driver for the entire AM5 platform) to at least version 5.01.03.005, and having a current version of Windows 10 or 11 on top of that. But there is also a fourth component – the use of the so-called Game Mode in Windows and the Xbox Game Bar as an aid (you need version 5.823.1271.0 or later). These are important because AMD has tied controlling which cores games are assigned to to this Windows widget.

The board BIOS and drivers are important because the board BIOS (UEFI) communicates to the operating system via the CPPC2 interface (you must have it enabled) the order of priority of cores for purpose of process scheduling – normally the ones that reach the highest clock speeds are preferred. However, with the Ryzen 9 7900X3D and Ryzen 9 7950X3D processors, the priority needs to be changed in favour of the V-Cache cores when gaming. And this is what the driver does by detecting when games are running and dynamically switching the firmware during gameplay to tell Windows to prioritize the cores on the chiplet with V-Cache.

Why Xbox Game Bar?

In most cases this should be automatic. The driver will automatically switch to V-Cache when Game Mode is active in Windows (or also Mixed Reality mode). Hence the use of the Xbox Game Bar. You have this tool preinstalled in Windows 10 and 11, unless you’ve somehow forcefully uninstalled it, and it’s most easily invoked by pressing the keys Windows + G.

The Xbox Game bar has a list of different games that it identifies and turns on Game Mode for them automatically, which also ensures that they are placed on V-Cache cores. Alongside this, however, the Xbox Game Bar also serves as a tool that you can use to correct the auto-detection if it fails. If your game isn’t detected, open the Xbox Game Bar, where you can click “this is a game” to add the program to the list. AMD drivers will then respond automatically.

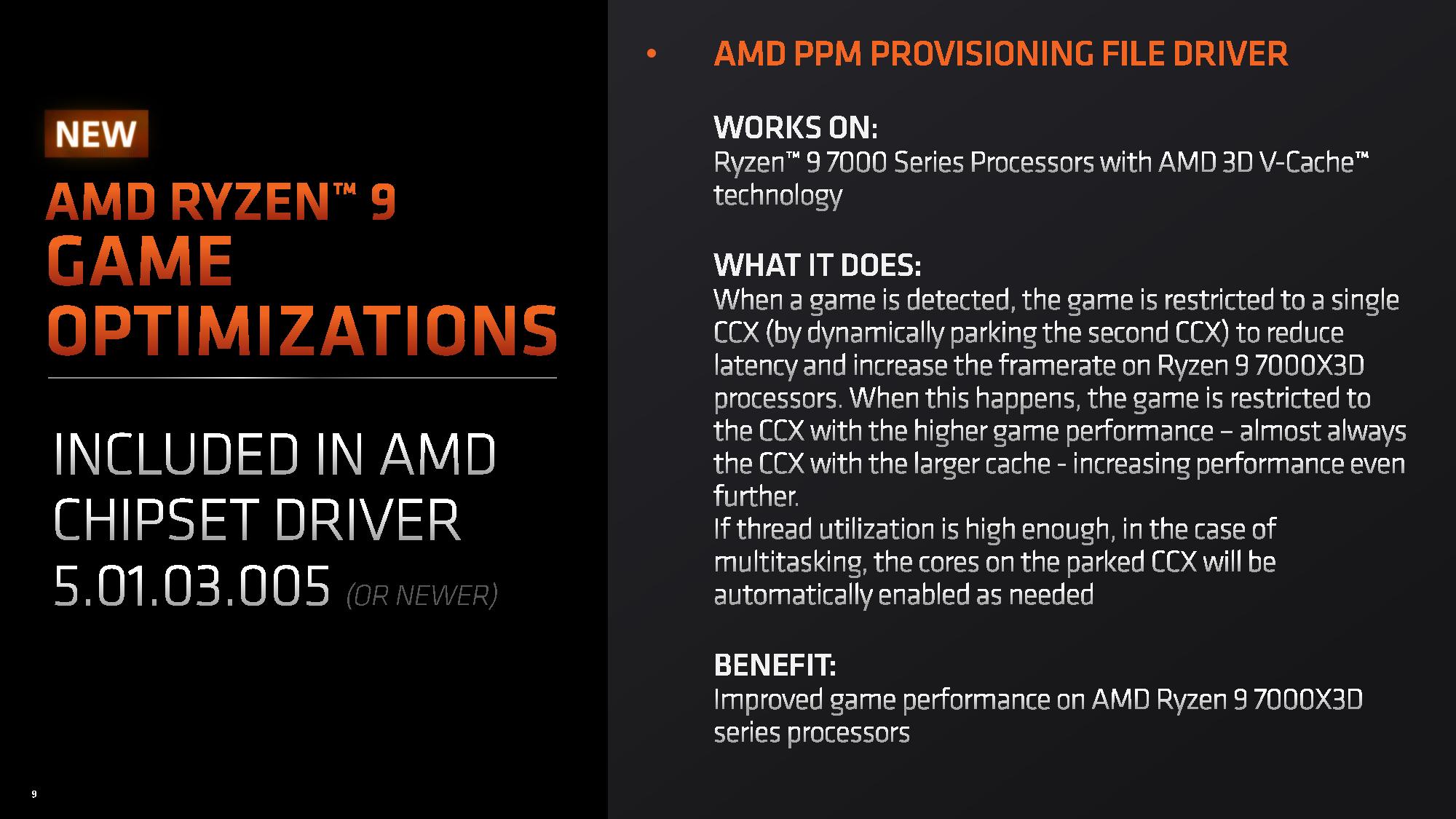

In addition to this functionality, you can also tweak or override the switching criteria in BIOS of the boards (as leaked before the release). AMD platform/chipset drivers also install the so-called AMD PPM Provisioning File Driver, which parks those cores that do not have V-Cache when Game Mode is active (parking a core means that Windows won’t schedule processes to it). This ensures that the game doesn’t spill to the other chiplet and in at least some cases should improve performance by keeping the application within the 3D V-Cache. This is because using cores from different chiplets makes inter-thread latency worse. Conversely, if the game is actually running on the chiplet without V-Cache (because it is more suited to high clock speeds), cores on the V-Cache chiplet are parked.

AMD also mentions that this performance management in games may not be accurate if VBS (Virtualization-based Security) is active in Windows, so it may be optimal to disable it, even though you are sacrificing one of the security barriers against malware and attacks. However, VBS always degrades performance a bit, so it’s possible that hardcore gamers would turn it off anyway, rendering the issue moot.

Ryzen 7 7800X3D doesn’t need special handling

If this seems overcomplicated, there is one potential relief. All of this only applies to the asymmetric dual-chiplet models, the Ryzen 9 7900X3D and 7950X3D. You won’t need any of this with the cheaper octa-core Ryzen 7 7800X3D, which comes out in April. That one has just one chiplet, all the cores are in it, and they all sit on one unified V-Cache. No game detection or matching will be needed and the processor will run fully without needing any such tricks.

The downside is that it won’t provide any high clock speed cores for non-gaming tasks. However, the fact that it will never use extreme clock speeds and voltages is should also be reflected in the power draw, so this has advantageous side effects too. The Ryzen 7 7800X3D should be very efficient.

Sources: Tom’s Hardware (1, 2, 3)

English translation and edit by Jozef Dudáš

⠀