Floating point a SIMD část

Minulý měsíc AMD vydalo procesory Ryzeny 5000. Jejich architektura Zen 3 přinesla nakonec možná víc, než se čekalo, výkon na 1 MHz někde převyšuje i IPC nejnovějšího jádra Intelu Willow Cove (Tiger Lake). Zen 3 je podle AMD jeho největší překopání architektury od vůbec prvního Zenu, pročež se podíváme, jaké změny v něm inženýři provedli, aby dokázali porazit Intel i v jednovláknovém a herním výkonu.

FPU: šest místo čtyř portů, také nové schedulery

Procesory AMD mají dlouhodobě vykonávání operací FPU a SIMD vyčleněné do oddělené FPU části (dost možná proto, že tyto operace pracují na odlišnou sadou registrů). Toto Intel nedělá, jeho unifikovaný scheduler zásobuje jak ALU část, tak FPU. Výhoda Intelu je asi efektivnější využití scheduleru, výhoda AMD je asi ta, že ALU a FPU operace mezi sebou nebojují o volné porty (u Intelu jsou jednotky pro ALU i SIMD/FPU operace prováděné na stejných portech).

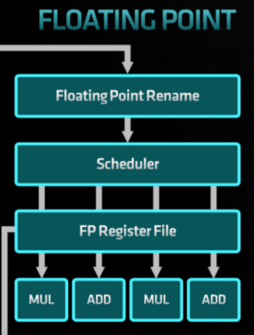

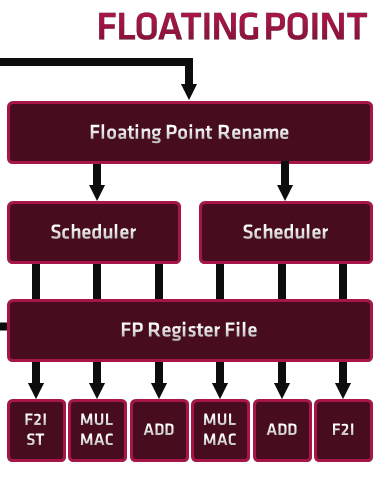

FPU měla na rozdíl od celočíselné části u předchozích jader Zen/Zen 2 vlastní unifikovaný scheduler. Zen 3 to ovšem také mění, vypadá to, že AMD udělalo podobnou reorganizaci jako v ALU. Místo jednoho scheduleru používá FPU zdá se nyní dva, ale opět jsou separátní od ALU/AGU schedulerů.

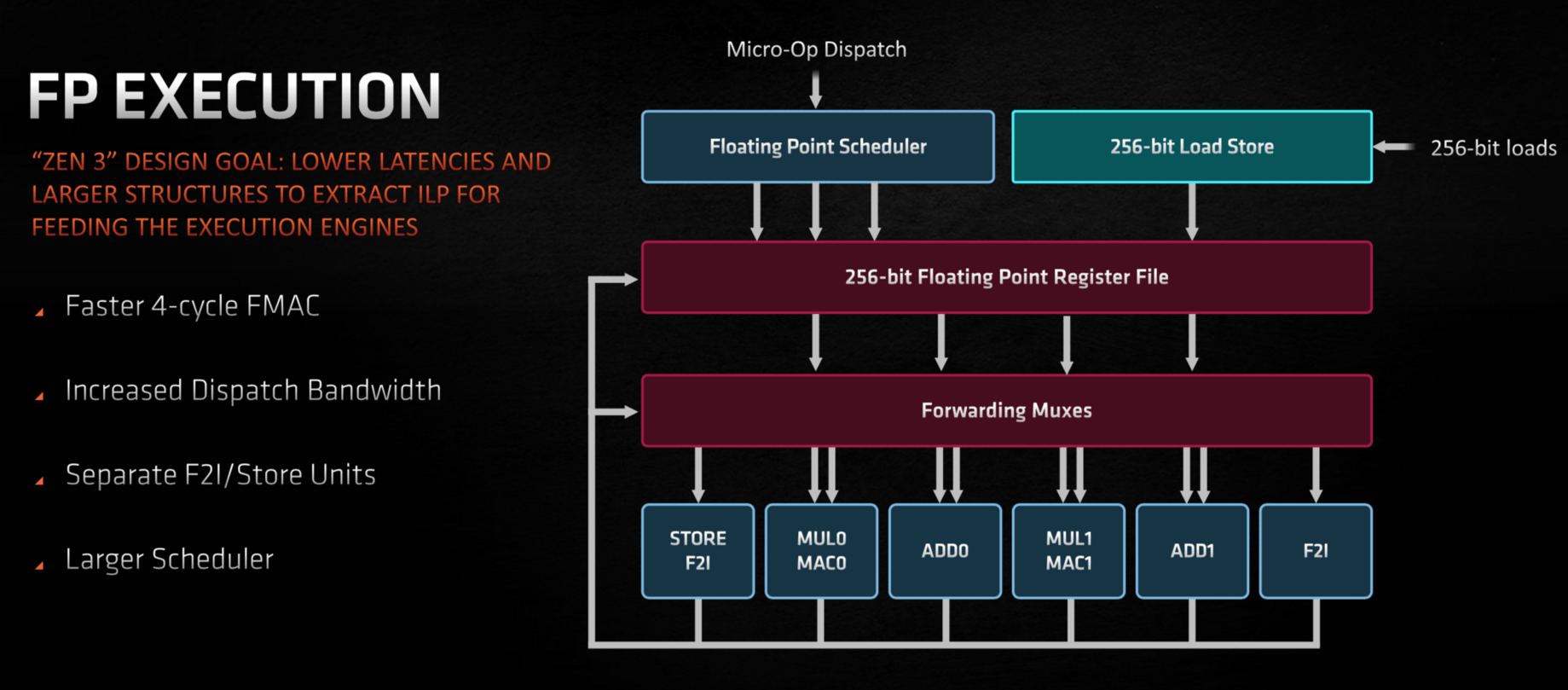

AMD dál aplikovalo i ono předělání portů, takže i zde je architektura výrazně změněná. Místo čtyř portů Zenu 1/2 má Zen 3 jednotky rozdělené mezi šest portů. Přímo kapacita výpočtů, tedy kolik lze provést operací FMA za takt, kolik sčítání a násobení, se asi nezměnila. Ale protože jsou tyto jednotky rozděleny mezi více portů, lze se častěji vyhnout blokování kvůli konfliktům, kdy by program chtěl paralelně provést dvě instrukce, ale obě jsou na stejném portu, takže jedna musí počkat. Například by měly být na samostatné porty přesunuté konverze dat z floating-point dat na celočíselná a operace FPU store, aby tyto jednodušší akce neblokovaly výpočetní instrukce.

Každý ze dvou schedulerů obsluhuje tři porty. První port má jednotky zpracovávající (F)MAC a násobení, druhý port má jednotky jen sčítání a podobné jednodušší operace. Na třetím jsou ony konverze dat nebo store operace.

Nejen v tom je FPU změněná, AMD snížilo latenci operací FMAC z 5 na 4 cykly, což by mělo zlepšit výkon, když na sobě operace závisí. Toto zlepšení latencí by jinak mělo být uplatněno i u některých dalších instrukcí (přehed změn v latencích a počtu uperací proveditelných za cyklus pro tyto instrukce má v tomto článku AnandTech). V SIMD operacích byla přidána podpora pro vektorové operace (de)šifrování – VAES a VPCLMULDQ nad 256bitovými registry (AVX/AVX2), které by měly výkon těchto šifer zlepšit až dvojnásobně proti 128bitovým operacím. Ovšem jen tehdy, pokud je program použije. Zen 3 také odstraňuje pomalost operací PDEP a PEXT patřících do rozšíření BMI2. Zen 1 a Zen 2 tyto instrukce totiž prováděly mikrokódem, což bylo pomalé, kdežto Zen 3 je už zvládá s vysokým (až o dva řídy lepším) výkonem. Mimochodem: nedávno se objevily spekulace, že pomalost těchto instrukcí je důvod, proč Zen 2 nemůže podporovat Smart Access Memory. Tyto věci spolu ale nesouvisí, AMD to dementovalo.

Celkově změny ve výpočetních jednotkách (ALU i jednotky v FPU) podle měření/profilování AMD dosahují zlepšení výkonu na 1 MHz asi o 3,3 % (z celkových 19 %).

⠀

- Contents

- AMD Zen 3: nová architektura, Op cache a frontend

- Překopaný výpočetní backend ALU a load/store

- Floating point a SIMD část

- Cache a velká změna s 8jádrovým CCX

- Jak velké je výšení IPC a koncepce Zenu 3

Moc pekny clanek. Diky JO 🙂

Zdravím, taková otázka na autora. Můžem čekat více článků od tebe na tomto webu, vzhledem k situaci s cnews. Nebo jsou nějaké jiné plány?

klikni na autora auvidíš, koľko tu má článkov a budeš prekvapkaný, aký dlhý čas už!

Bez ohľadu na to, ako to dopadne so Cnews (verím, že pozitívne a čoskoro bude fungovať tak ako predtým), tak by Jano mal vo väčšom objeme vydávať články aj u nás. Celkovo sa na HWC čoskoro dočkáte veľkých zmien, na ktoré sa už pripravujeme dlhší čas a štart je blízko. 🙂

těšíme se… 🙂

číta sa to dobre, paráda, díkes 🙂

ešte tak prilákať Vítka a Rybku!