Výpočetní jednotky: 17 portů, potenciál pro vysoké IPC

Intel teď odhalil architekturu svých nejnovějších procesorů Alder Lake. Tentokrát jsou to ale architektury dvě. Alder Lake je hybridní a vedle „velkých“ jader pro jednovláknový výkon má další „malá“ jádra Gracemont. Ta ale nejsou jen do počtu či pro úsporu energie v nečinnosti jako u ARMů v mobilech, naopak se významně podílí na celkovém výkonu. Jejich architektura je vlastně sama celkem velká a teď se na ní detailně podíváme.

Totéž se asi dá říct o samotném backendu výpočetních jednotek. Tam totiž Intel hodně přidal na výpočetních portech, do kterých jsou jednotky organizovány. Paradoxně má dokonce Gracemont teď víc portů, než Golden Cove. To je ale proto, že Golden Cove má unifikovaný scheduler pro AGU, ALU i FPU/SIMD operace a ALU a SIMD má rozmístěno na stejných pěti portech. Naproti tomu Gracemont používá podobnou koncepci jako AMD a má rozdělené jednotky ALU a AGU, které pracují s obecnými x86 registry, a separátně pak jsou na svých vlastních portech jednotky FPU/ SIMD, které pracují nad vektorovými registry YMM, XMM (a legacy x87).

Zatímco Tremont měl 10 portů, Gracemont má o dost víc výpočetních i AGU a FPU/SIMD jednotek a kvůli tomu je portů dokonce 17 (Golden Cove jich má díky onomu sdílení portů jen 12). Počet ALU stoupl ze tří v Tremontu na čtyři (jako má Zen 3; Golden Cove má pět). Z těchto čtyř dvě umějí jen jednodušší operace typu sčítání, posuv a logické operace. Navíc i násobení a celočíselné skalární dělení umějí zbylé dvě z ALU – tyto operace tedy lze provést dvě za cyklus, jednodušší instrukce čtyři za cyklus. ALU jsou na portech 0, 1, 2 a 3.

Gracemont má separátní jednotky pro výpočet větvení (JMP), které tak neobtěžují jednotky ALU. Tyto jednotky mají dva vlastní porty, označené 30 a 31. Jádro tak dokáže zpracovat dvě větvení za cyklus, zatímco Tremont uměl jen jedno.

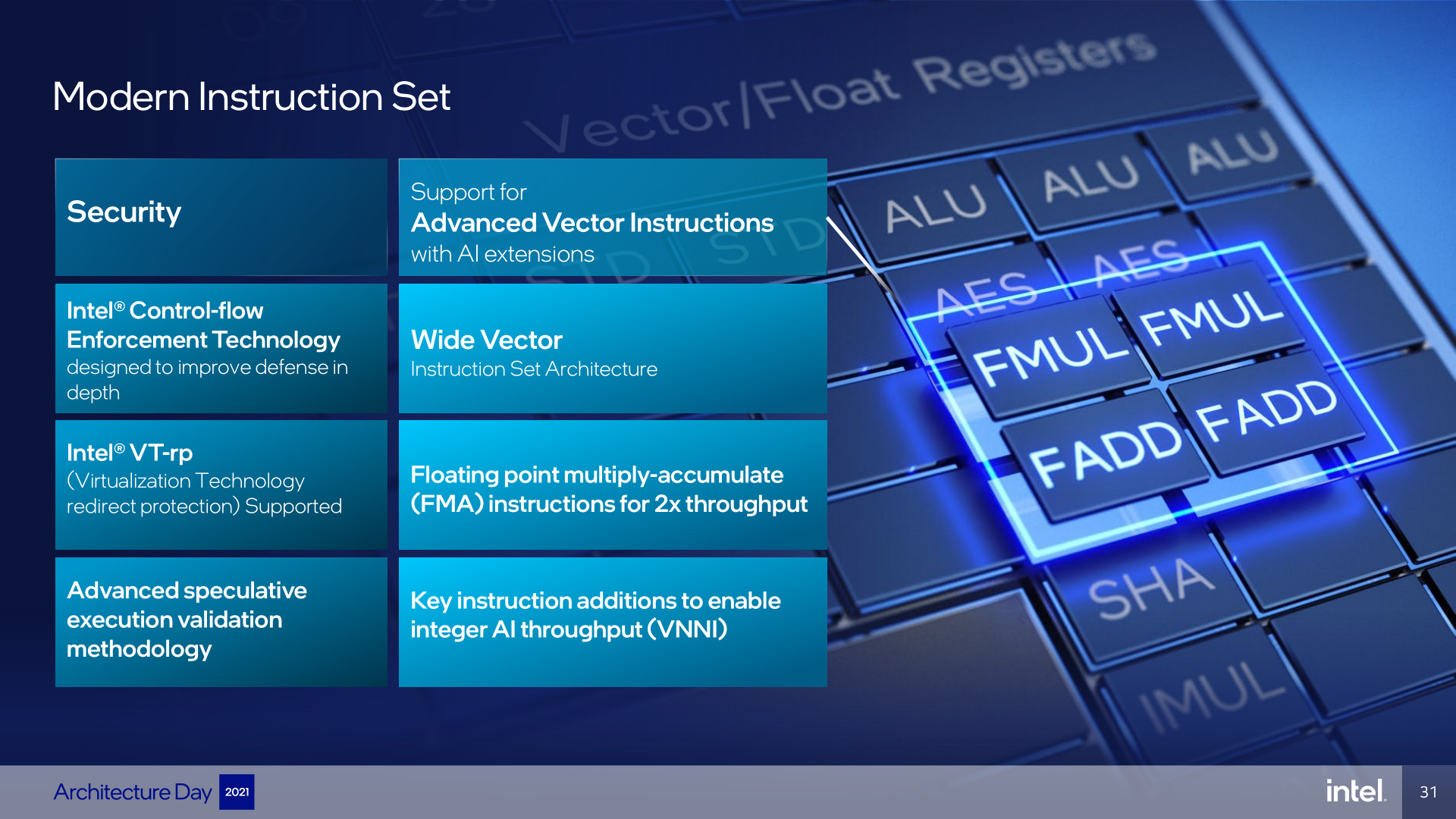

FPU (SIMD): AVX a AVX2, VNNI

Ona separátní část s jednotkami FPU/SIMD zabírá pět portů – z nich dva (28, 29) slouží jen pro ukládání dat ze SIMD registrů podobně jako skalární Store Data pipeline. Výpočetní SIMD jednotky jsou na třech portech (20, 21, 22) a Gracemont na nich má dvě symetrické pipeline pro floating-point SIMD instrukce, které umí sčítání (FADD), násobení (FMUL) a také akceleraci AES. Floating-point dělička je jen na jedné pipeline, stejně jako jednotka pro akceleraci kryptografického algoritmu SHA. Oproti Tremontu je floating-point výkon až dvojnásobný (s výjimkou dělení), jelikož v jeho případě měla FPU sice dva porty, ale celkem jen jednu jednotku FADD a jednu FMUL.

Celočíselné SIMD operace (užitečné například pro multimédia, ale i další obecnější úlohy) umí dokonce tři jednotky (oproti dvěma v Tremontu), ovšem zase to platí jen pro ty jednodušší instrukce. Celočíselné SIMD násobení je jako v Tremontu jen na jednom portu.

Velká novinka je, že Gracemont podporuje instrukce AVX a AVX2, tedy 256bitové vektorové operace jak nad celočíselnými, tak nad floating-point daty. Intel nezmiňuje, zda se tyto operace vykonávají v jediném cyklu, tedy zda jsou ony dvě, respektive tři jednotky nativně 256bitové. To by už kladlo Gracemont hodně blízko spotřebitelské verzi Golden Cove, která má vypnuté AVX-512, takže bych spíš čekal, že vykonávání bude po dvou 128bitových polovinách. Tak je to například u AMD Zenu 1 a znamená to poloviční teoretický výkon v AVX a AVX2, v praxi ale zpomalení programů často bývá méně drastické.

Díky podpoře AVX a AVX 2 je možné používat na Alder Lake tyto užitečné instrukce místo toho, aby musely být u velkých jader Golden Cove deaktivované, jako se to stalo u hybridního procesoru Lakefield. Zmíněno je i rozšíření FMA, takže i to bude Alder Lake jako celek podporovat.

Poměrně důležité by mělo být, že Gracemont podporuje instrukce VNNI zřejmě nad 256bitovými instrukcemi místo 512bitových), což umožňuje použití stejného rozšíření i u Golden Cove v procesorech Alder Lake. Toto rozšíření je užitečné pro akceleraci neuronových cítí (aplikace umělé inteligence), byť jeho výkon bude v této omezenější formě trošku nižší, než u jader s AVX-512.

Z dalších už ne SIMD rozšíření Gracemont také podporuje bezpečnostní funkci Control-flow Enforcement Technology, která měla premiéru v procesorech Tiger Lake a VT-rp (Virtualization Technology redirect protection). Jádro by prý mělo být poměrně odolné proti různým side-channel bezpečnostním zranitelnostem a útokům.

Článek pokračuje další kapitolou.

- Contents

- Velká a „malá“ jádra: proč vůbec?

- Gracemont: „malá“(?) architektura silná už jako Skylake

- Výpočetní jednotky: 17 portů, potenciál pro vysoké IPC

- Paměťový subsystém: Dvakrát víc AGU a Load/Store

- Rychlost: „Malé“ jádro má až dvě třetiny výkonu velkého