Last week, alleged leaks painted the future high-end Ryzen 9 processor lineup in AMD’s upcoming 5nm CPU generation. Now an actual sample of Zen 4 has surfaced – someone tested it in Geekbench and the result made it into the public database. This is apparently the first ever such leak, which may illustrate some of the architectural changes AMD is planning in the new cores.

Although we have what is probably the first Zen 4 performance score from this leak, not that the scores themselves are of marginal utility. This is because we’re talking about an early engineering sample that runs at frequencies well below what the processors should achieve in the final version. The base clock speed of the processor was only 1.2 GHz – such a low number also corresponds to the fact that this is not a sample of a desktop Ryzen processor, but a server version, namely the Epyc 7004 “Genoa”. Early server CPU samples have generally had such low clock speeds.

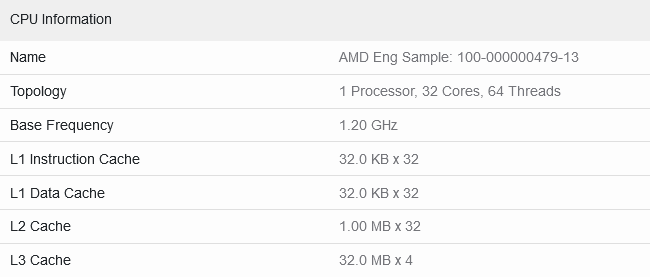

Epyc 7004s will have up to 96 Zen 4 cores in 12 CPU chiplets manufactured on a 5nm process. However, the 100-000000479-13 sample is only 32-core, and with 64 threads. So as you can see, Zen 4 still uses SMT with two threads per core. The processor was tested on a development board labelled AMD Quartz and used 32 GB of memory (probably DDR5).

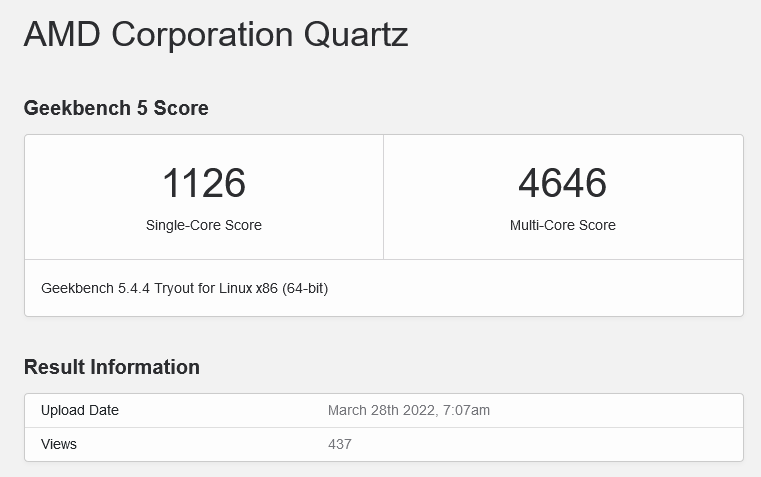

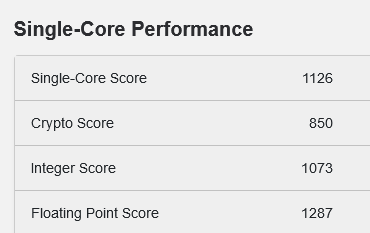

AMD server processor sample with Zen 4 architecture in Geekbench (Source: Geekbench)

Although the Geekbench snapshot shows a clock speed of 1.2 GHz, that’s just the base clock speed. In reality, the CPU seems to have run at much higher clock speeds during the test, Geekbench detected a frequency of around 3430 MHz (so the CPU boost could probably be 3.45 GHz), which is not too low for a first generation sample (ES0). It is in this context that the score should be taken – 1126 points in the single-threaded test and 4646 in the multi-threaded one. Especially the second number is very low for a 32-core processor, but it’s probably all due to using an immature platform, where memory performance in particular could still be very poor. These numbers can’t really be used to conclude about how good (or bad) the final Zen 4 will be.

The interesting parts are mainly the captured parameters and the very proof that Zen 4 processor samples are not only running and being tested, but are no longer a closely guarded secret. It seems there are now enough people already testing them outside of AMD for such records to get out (this is what happens when someone runs the unpaid version of Geekbench (with an internet connection), where the results are sent automatically to the database).

Zen 4 has bigger L2 cache, AMD didn’t touch L3 and L1

Parameters detected by Geekbench have shown us what cache will the Zen 4 processors have. The L1 cache doesn’t seem to be getting any bigger – AMD will keep it at just 32 KB L1 Cache for data with Zen 4 as well. At least we can hope that its latency won’t get worse. Also, the instruction L1 cache will remain 32 KB too. Unfortunately, Geekbench won’t reveal what the µOp cache capacity will be.

However, the database confirms one architectural change. All cores in the Zen to Zen 3 line till now had used 512 KB L2 cache dedicated to one core, but Zen 4 will change this and have 1MB L2 cache for each core, according to this database entry. This means that more data will fit in it, so some tasks that have a working data sate large enough to no fit in the 512 KB cache (but not significantly larger than 1 MB) could benefit handsomely. According to simulations recently performed by the Chips and Cheese website, increasing the cache from half to a full megabyte can improve performance (IPC, i.e., performance per 1 MHz) by quite a bit, although it will depend on whether the larger cache capacity doesn’t slow things down too much. AMD has so far had a very low latency of 12 cycles for its L2 cache, which also helped performance. We do not yet know what price the core will pay for the doubled capacity.

The 1MB L2 cache confirmation seems to indicate that the information about the Zen 4 architecture leaked last summer was probably true. What wasn’t in them then, and we’re learning now, though, is the capacity of the L3 cache. This will seemingly be unchanged from Zen 3. The Genoa processor sample has a total of 128MB of L3 cache in four 32MB blocks. So, as with the Epyc 7003 Milan, the CPU will be organized as consisting of octa-core CCX blocks that have their own associated shared L3 Cache block, which will again be 32MB. So this is “nothing new really” type of information, but since we didn’t know aynthing about the Zen 4’s L3 before this, it is still a valuable finding.

The Ryzen 7000 desktop processors will be based on the same CPU chiplets as the server CPUs, so the same will apply to them. This means Ryzen 7000 processors with eight cores or less will have 32MB of L3 cache and presumably one CCX. Models with more cores (up to 16, which will probably be the maximum) will have a pair of CCX (and thus CPU chiplets) and 2×32MB L3 Cache.

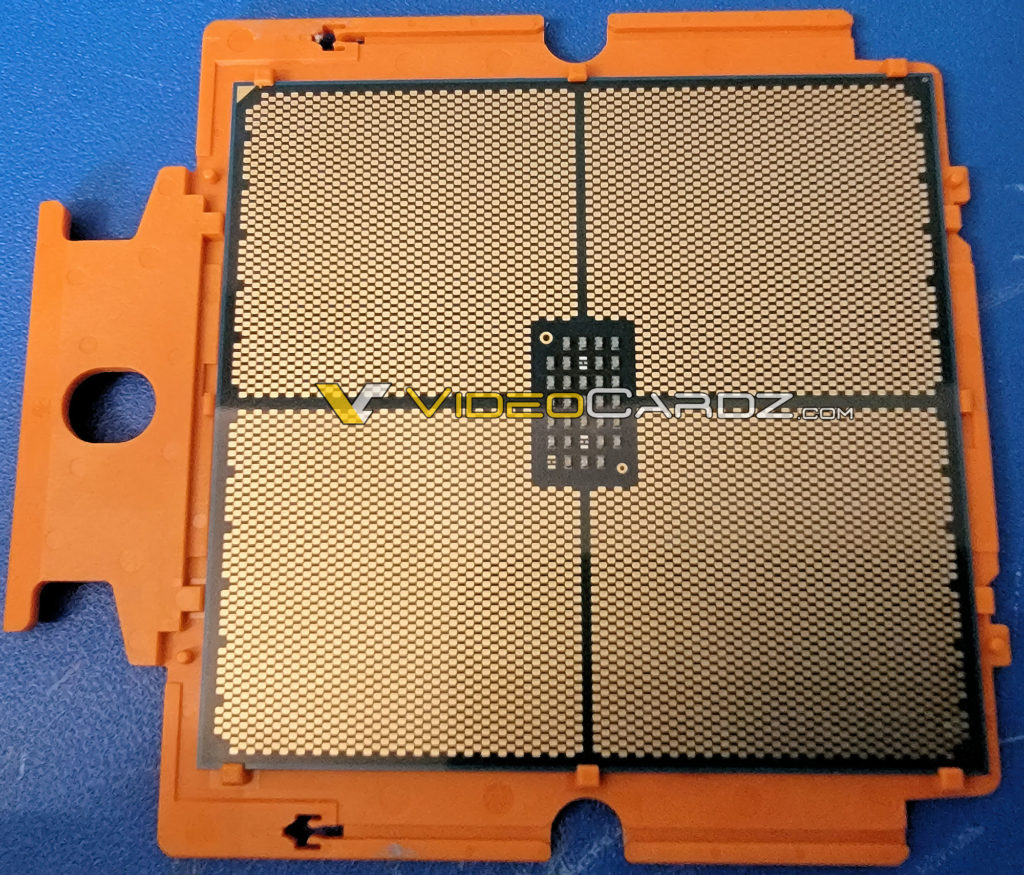

Tip: AM5 socket and Ryzen 7000 shown. Zen 4 capable of 5 GHz all-core

Sources: Geeekbench, Benchleaks, VideoCardz

English translation and edit by Jozef Dudáš, original text by Jan Olšan, editor for Cnews.cz

⠀