For a long time, Moore’s Law meant new technologies provided more transistors for the same or lower cost, as more could fit onto a chip of the same size. But in the last decade, production costs have been rising, transistors are no longer getting cheaper, and same-sized chips are costing more. And after the 2nm process, things will escalate dramatically – a single wafer will cost nearly ten times more than it did ten years ago.

Taiwanese site China Times published information on pricing for TSMC’s upcoming manufacturing nodes last week. The pricing is something the company doesn’t advertise directly, and exact numbers are part of individual offers and negotiations, as is typical in the space of B2B services and products. Nevertheless, it’s possible to estimate a ballpark figure for a fabricated silicon wafer (which is a 300mm-diameter disc from which chips are made), around which contractual prices will likely revolve.

Wafer pricing is a problem

The issue with modern manufacturing processes is that the wafer itself remains the same size (meaning the number of final dies made from it stays similar for a given chip area), but its price keeps going up. While manufacturing a wafer used to cost under $5,000 ten years ago, prices have been steadily rising since the advent of FinFET nodes and later the EUV technology. And to make matters worse, these new processes no longer deliver the same transistor density improvements they provided in the past. According to China Times, the cost of a wafer on the 2nm N2 process is around $30,000, while for the 3nm node, it’s estimated between 18,000 USD and 20,000 USD.

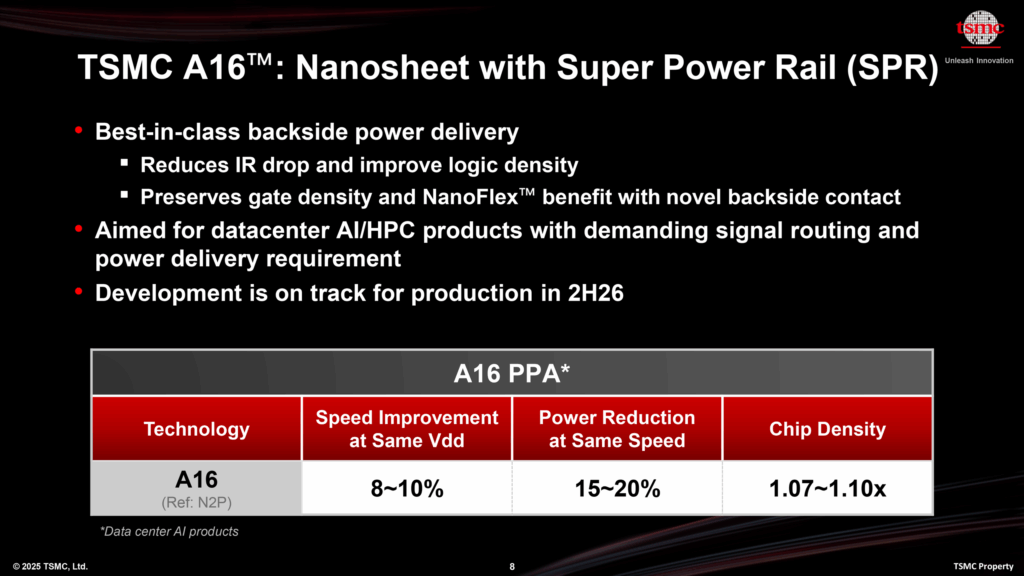

The price for the next-generation 1.6nm process (A16 technology) is expected to jump by another 50%. TSMC is reportedly considering charging up to 45,000 USD per wafer. If CPU and GPU manufacturers produce chips of the same die size, their silicon costs would increase by the same proportion. This would likely affect end-user prices, although the final product includes many components, so we might not feel the full 50% increase directly.

This trend of rising costs in cutting-edge technologies may lead to broader use of chiplet architectures, with the most advanced process nodes being used only for smaller portions of a CPU, SoC, or GPU, with other parts increasingly being disaggregated into silicon built with older and cheaper process nodes.

Price increases have accelerated sharply

To understand how dramatically chip manufacturing costs have risen, consider estimates published by Tom’s Hardware. Until about a decade ago, prices remained relatively low, making the latest nodes fairly accessible. In 2004, a wafer produced on TSMC’s 90nm process cost 2,000 USD. By 2014, a 28nm wafer cost 3,000 USD – but this increase occurred gradually across several generations and “half-node” steps (80nm, 65nm, 55nm, 40nm generations).

In 2016, the 10nm process cost 6,000 USD. Two years later, 7nm wafers cost $10,000. Another two years on, 5nm wafers reached 16,000 USD, and the current 3nm process has pushed that to 18,000–20,000 USD per wafer. We now face a projected 50% markup every two years, which is roughly the cadence of new process generation introductions.

Despite the skyrocketing costs, competitive pressure still continues to push chipmakers toward adopting the most advanced nodes for now (and they’ll probably have to pass those costs on to end users). Besides Apple, MediaTek will also produce chips on the 2nm node, and AMD has confirmed its plans as well.

Fujitsu is reportedly preparing its own chips on this technology (likely for expensive server and HPC hardware, not consumer products). Qualcomm’s new Snapdragon 8 Elite will also be made on this node, as will proprietary chips from companies like Microsoft (the Maia 300 AI accelerator), Google (8th-gen TPU), and Amazon (Trainium 4). TSMC is reportedly aiming to offer production volume of 30,000 wafers per month on the 2nm process by the end of the year.

It’s not just the per-chip manufacturing cost that’s becoming a luxury – fixed costs for developing and ramping up production of a chip are also rising. According to China Times, the full process of developing and preparing a 2nm chip could cost up to $725 million. That’s money that must be recovered from product margins – and it is yet another factor that will contribute to raised prices of products that we as consumers ultimately pay.

Sources: China Times, Tom’s Hardware

English translation and edit by Jozef Dudáš

10240;

Please use process names and don’t try to translate those to nm. As process names haven’t been direcctly connected to litography node size for almost a decade.

Check Ian Curtress for more info.

“As process names haven’t been direcctly connected to litography node size for almost a decade.”

What you probably mean is that *nominal* litography node sizes have not connected to the actual physical sizes of the features on the etched chip. That probably was the case for an even longer time.

However, we are not discussing actual transistor/gate/pitch dimensions at all. We are only discussing the process nodes as overall packages themselves. All the companies still use process names that are basically nanometer numbers. So any “litography node” today is still a nanometer number. N3 means 3 in nanometer scale, 3. A16 means 16 in ångström scale (which is 1.6 nm). Intel’s A18 or A14 is the same thing, it clearly is meant to imply 1.8 nm and 1.4 nm.

And that is why we aren’t rigid about the names and still also use the simplified nanometer numbers to refer to process nodes. It is a common usage used everywhere, including by the industry. Those numbers are still functional for the purpose for now. We could use the names like N3 and A16 exclusively, but there isn’t really that much point to sticking to that rigidly.